Last update: @1/7/2023

•

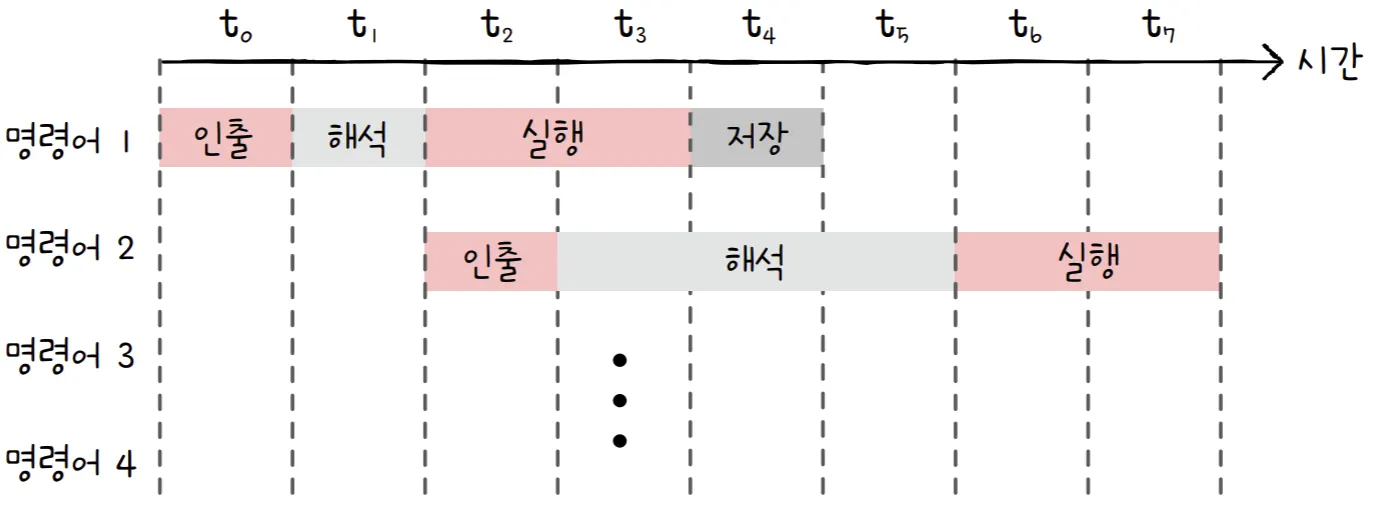

명령어 파이프라이닝과 슈퍼스칼라 기법을 실제로 CPU에 적용하려면 명령어가 파이프라이닝에 최적화되어 있어야 함

•

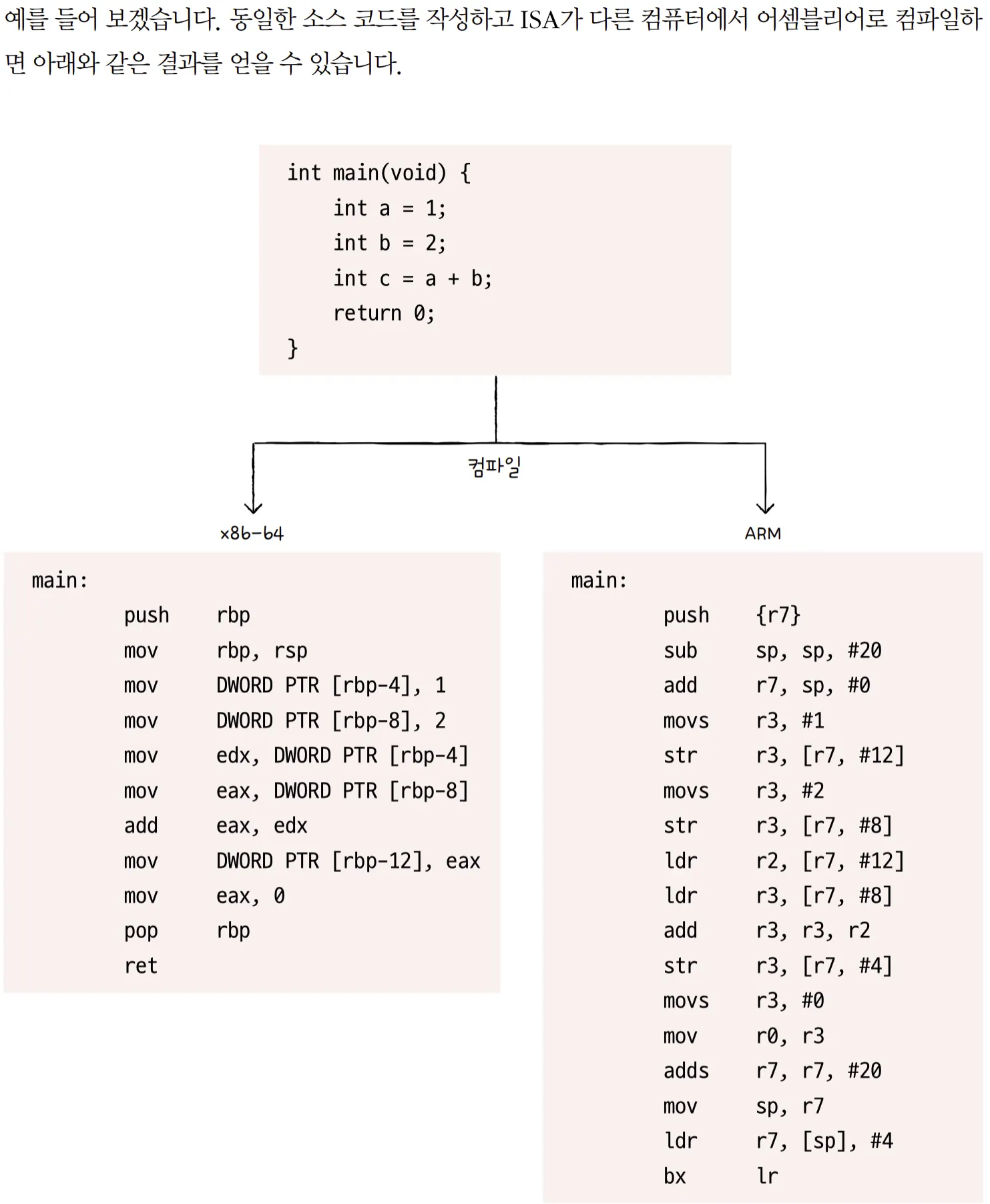

명령어 집합(instruction set = ISA; Instruction Seet Architecture(명령어 집합 구조))

: CPU가 이해할 수 있는 명령어들의 모음. 다른 ISA를 사용하는 CPU는 명령어, 어셈블리어가 모두 다름

◦

예시

▪

인텔 CPU는 x86 또는 x86-64 ISA를 이해함

▪

애플 CPU는 ARM ISA를 이해함

▪

참고로 사용한 컴파일러에 따라서도 어셈블리어가 달라질 수 있음

◦

ISA가 달라지만 제어장치가 명령어를 해석하는 방식, 사용되는 레지스터의 종류와 개수, 메모리 관리 방법 등 많은 것이 달라짐. 이는 곧 CPU 하드웨어 설계에도 큰 영향을 미침

◦

ISA는 CPU의 언어이자 하드웨어가 소프트웨어를 어떻게 이해할지에 대한 약속임

◦

명령어 병렬 처리 기법을 도입하기 유리한 ISA가 있고 그렇지 않은 IAS가 있음

◦

현대 ISA의 양대 산맥인 CISC와 RISC

▪

CISC(Complex Instruction Set Computer)

: ‘복잡한 명령어 집합을 활용하는 컴퓨터(=CPU)’를 의미. 복잡하고 다양한 명령어를 활용하는 CPU 설계 방식. x86, x86-64가 대표적

•

명령어의 형태와 크기가 다양한 가변 길이 명령어를 활용함

•

장점

◦

상대적으로 적은 수의 명령어로도 프로그램을 실행할 수 있음

◦

컴파일된 프로그램의 크기가 작음

•

메모리를 최대한 아끼며 개발해야 했던 시절에 인기가 높았음

•

단점

◦

명령어의 크기와 실행되기까지의 시간이 일정하지 않음

◦

복잡한 명령어 하나를 실행하는 데에 여러 클럭 주기를 필요로 하기 때문에 명령어 규격화가 어렵고, 명령어 파이프라인을 구현하는 데에 큰 걸림돌이 됨

◦

실제 대다수의 복잡한 명령어는 사용 빈도가 낮음

•

CISC의 한계가 준 교훈

◦

빠른 처리를 위해 명령어 파이프라인을 십분 활용해야 함. 원활한 파이프라이닝을 위해 ‘명령어 길이와 수행 시간이 짧고 규격화’되어 있어야 함

◦

2 어차피 자주 쓰이는 명령어만 줄곧 사용됨. 복잡한 기능을 지원하는 명령어를 추가하기보다는 ‘자주 쓰이는 기본적인 명령어를 작고 빠르게 만드는 것’이 중요함

▪

RISC(Reduced Instruction Set Computer)

: CISC에 비해 명령어의 종류를 줄이고, 짧고 규격화된 명령어, 되도록 1클럭 내외로 실행되는 명령어를 지향한 IAS. 즉, RISC는 단순하고 적은 수의 고정 길이 명령어를 활용함

•

메모리에 직접 접근하는 명령어를 load, store 두 개로 제한할 만큼 메모리 접근을 단순화하고 최소화를 추구함. 그렇기 때문에 CISC보다 주소 지정 방식의 종류가 적은 경우가 많음

◦

이런 점에서 RISC를 load-store 구조라고 부르기도 함

•

RISC는 메모리 접근을 단순화, 최소화하는 대신 레지스터를 적극적으로 활용함. 그렇기에 CISC보다 레지스터를 이용하는 연산이 많고, 일반적인 경우보다 범용 레지스터 개수도 더 많음

•

사용 가능한 명령어 개수가 CISC보다 적기 때문에 RISC는 CISC보다 많은 명령으로 프로

그램을 작동시킴

▪

CISC와 RISC 차이 정리